在嵌入式應用中,系統的功耗越來越受到人們的正視,這一點對于需要電池供電的便攜式系統尤其顯著。降低系統功耗,延長電池的壽命,就是降低系統的運行本錢。對于以單片機為核心的嵌入式應用,系統功耗的最小化需要從軟、硬件設計兩方面入手。

跟著越來越多的嵌入式應用使用了實時操縱系統,如何在操縱系統層面上降低系統功耗也成為一個值得關注的題目。限于篇幅,本文僅從硬件設計和應用軟件設計兩個方面討論。

1 硬件設計

選器具有低功耗特性的單片機可以大大降低系統功耗。可以從供電電壓、單片機內部結構設計、系統時鐘設計和低功耗模式等幾方面考察一款單片機的低功耗特性。

1.1 選用盡量簡樸的CPU內核

在選擇CPU內核時切忌一味追求機能。8位機夠用,就沒有必要選用16位機,選擇的原則應該是“夠用就好”。現在單片機的運行速度越來越快,但機能的晉升往往帶來功耗的增加。一個復雜的CPU集成度高、功能強,但片內晶體管多,總漏電流大,即使進入STOP狀態,漏電流也變得不可忽視;而簡樸的CPU內核不僅功耗低,本錢也低。

1.2 選擇低電壓供電的系統

降低單片機的供電電壓可以有效地降低其功耗。當前,單片機從與TTL兼容的5 V供電降低到3.3 V、3 V、2 V乃至1.8 V供電。供電電壓降下來,要歸功于半導體工藝的發展。從原來的3 μm工藝到現在的0.25、0.18、0.13 μm工藝, CMOS電路的門限電平閾值不斷降低。低電壓供電可以大大降低系統的工作電流,但是因為晶體管的尺寸不斷減小,管子的漏電流有增大的趨勢,這也是對降低功耗不利的一個方面。

目前,單片機系統的電源電壓仍以5 V為主,而過去5年中,3 V供電的單片機系統數目增加了1倍,2 V供電的系統也在不斷增加。再過五年,低電壓供電的單片機數目可能會超過5 V電壓供電的單片機。如斯看來,供電電壓降低將是未來單片機發展的一個重要趨勢。

1.3 選擇帶有低功耗模式的系統

低功耗模式指的是系統的等待和休止模式。處于這類模式下的單片機功耗將大大小于運行模式下的功耗。過去傳統的單片機,在運行模式下有wait和stop兩條指令,可以使單片機進入等待或休止狀態,以達到省電的目的。

等待模式下,CPU休止工作,但系統時鐘并不休止,單片機的外圍I/O模塊也不休止工作;系統功耗一般降低有限,相稱于工作模式的50%~70%。

休止模式下,系統時鐘也將休止,由外部事件間斷重新啟動時鐘系統時鐘,進而喚醒CPU繼承工作,CPU消耗電流可降到μA級。在休止模式下,CPU本身實際上已經不消耗什么電流,要想進一步減小系統功耗,就要盡量將單片機的各個I/O模塊關掉。跟著I/O模塊的逐個封閉,系統的功耗越來越小,進入休止模式的深度也越來越深。進入深度休止模式無異于關機,這時的單片機耗電可以小于20 nA。其中特別要提示的是,片內RAM休止供電后,RAM中存儲的數據會丟失,也就是說,喚醒CPU后要重新對系統作初始化。因此在讓系統進入深度休止狀態前,要將重要系統參數保留在非易失性存儲器中,如EEPROM中。深度休止模式關掉了所有的I/O,可能的喚醒方式也很有限,一般只能是復位或IRQ間斷等。

留存的I/O模塊越多,系統答應的喚醒間斷源也就越多。單片機的功耗將根據留存喚醒方式的不同,降至1μA至幾十μA之間。例如,用戶可以留存外部鍵盤間斷,留存異步串行口(SCI)接收數據間斷等來喚醒CPU。留存的喚醒方式越多,系統耗電也就會多一些。其他可能的喚醒方式還有實時鐘喚醒、看門狗喚醒等。停機狀態較淺的情況下,外部晶振電路仍是工作的。

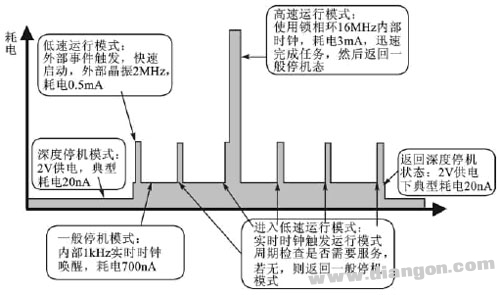

圖1以Freescale的HCS08單片機為例,給出不同運行模式下的系統功耗。HCS08是8位單片機,有多個系列,各系列I/O模塊數量有所不同,但低功耗模式下的電流消耗大致相同。

圖1HCS08單片機各模式下的耗電

以R系列單片機為例:在室溫(25℃)下,不包括I/O口的負載,以2 V供電,將可編程鎖相環時鐘設為16 MHz(總線時鐘8 MHz),典型電流值為2.6 mA,當溫度升高到85℃時,供電電流也升高到3.6 mA;而采用3 V供電,這一組數據升高至3.8 mA和4.8 mA。用2 V供電,直接使用外部晶振2 MHz(總線時鐘1 MHz)時,典型運行電流降至450 μA。在等待狀態下,因時鐘并沒有休止,耗電情況和時鐘頻率有很大關系,節省的功耗有限;而進入輕度休止(stop3),以外部間斷喚醒,電流消耗在0. 5 μA左右。在中度休止態(stop2),功耗可進一步降低。使用內部1 kHz的時鐘,保持1個運行的時鐘,周期性喚醒CPU,所增加的電流約為0.3 μA。在深度休止態(stop1),RAM的數據也不再留存,只能通過外部復位重啟系統,此時的電流消耗可降到20 nA。以上數據都是在室溫下丈量所得。當環境溫度升高到85℃時,電流消耗可能增加3~5倍。

1.4選擇合適的時鐘方案

時鐘的選擇對于系統功耗相稱敏感,設計者需要留意兩個方面的題目:

第一是系統總線頻率應當盡量低。單片機內部的總電流消耗可分為兩部門——運行電流和漏電流。理想的CMOS開關電路,在保持輸出狀態不變時,是不消耗功率的。例如,典型的CMOS反相器電路,如圖2所示,當輸入端為零時,輸出端為1,P晶體管導通,N晶體管截止,沒有電流流過。而實際上,因為N晶體管存在一定漏電流,且隨集成度進步,管基越薄,漏電流會加大。溫度升高,CMOS翻轉閾電壓會降低,而漏電流則隨環境溫度的增高變大。在單片機運行時,開關電路不斷由“1”變“0”、由“0”變“1”,消耗的功率是由單片機運行引起的,我們稱之為“運行電流”。如圖2所示,在兩只晶體管互相變換導通、截止狀態時,因為兩只管子的開關延遲時間不可能完全一致,在某一瞬間會有兩只管子同時導通的情況,此時電源到地之間會有一個瞬間較大的電流,這是單片機運行電流的主要來源。可以看出,運行電流幾乎是和單片機的時鐘頻率成正比的,因此盡量降低系統時鐘的運行頻率可以有效地降低系統功耗。

第二是時鐘方案,也就是是否使用鎖相環、使用外部晶振仍是內部晶振等題目。新一代的單片機,如飛思卡爾的HCS08系列單片機,片內帶有內部晶振,可以直接作為時鐘源。使用片內晶振的長處是可以省掉片外晶振,降低系統的硬件本錢;缺點是片內晶振的精度不高(誤差一般在25%左右,即使校準之后也可能有2%的相對誤差),而且會增加系統的功耗。

現代單片機普遍采用鎖相環技術,使單片機的時鐘頻率可由程序控制。鎖相環答應用戶在片外使用頻率較低的晶振,可以很大地減小板級噪聲;而且,因為時鐘頻率可由程序控制,系統時鐘可以在一個很寬的范圍內調整,總線頻率往往能升得很高。但是,使用鎖相環也會帶來額外的功率消耗。

單就時鐘方案來講,使用外部晶振且不使用鎖相環是功率消耗最小的一種。

2 應用軟件方面的考慮

之所以使用“應用軟件”的說法,是為了區分于“系統軟件”或者“實時操縱系統”。軟件對于一個低功耗系統的重要性經常被人們忽略。一個重要的原因是,軟件上的缺陷并不像硬件那樣輕易發現,同時也沒有一個嚴格的尺度來判定一個軟件的低功耗特性。盡管如斯,設計者仍需盡量將應用的低功耗特性反映在軟件中,以避免那些“看不見”的功耗損失。

2.1 用“間斷”代替“查詢”

一個程序使用間斷方式仍是查詢方式對于一些簡樸的應用并不那么重要,但在其低功耗特性上卻相去甚遠。使用間斷方式,CPU可以什么都不做,甚至可以進入等待模式或休止模式;而查詢方式下,CPU必需不停地訪問I/O寄存器,這會帶來良多額外的功耗。

2.2 用“宏”代替“子程序”

程序員必需清晰,讀RAM會比讀Flash帶來更大的功耗。恰是由于如斯,低功耗機能凸起的ARM在CPU設計上僅答應一次子程序調用。由于CPU進入子程序時,會首先將當前CPU寄存器推入堆棧(RAM),在離開時又將CPU寄存器彈出堆棧,這樣至少帶來兩次對RAM的操縱。因此,程序員可以考慮用宏定義來代替子程序調用。對于程序員,調用一個子程序仍是一個宏在程序寫法上并沒有什么不同,但宏會在編譯時展開,CPU只是順序執行指令,避免了調用子程序。獨一的題目好像是代碼量的增加。目前,單片機的片內Flash越來越大,對于一些不在乎程序代碼量大一些的應用,這種做法無疑會降低系統的功耗。

2.3 盡量減少CPU的運算量

減少CPU運算的工作可以從良多方面入手:將一些運算的結果預先算好,放在Flash中,用查表的方法替換實時的計算,減少CPU的運算工作量,可以有效地降低CPU的功耗(良多單片機都有快速有效的查表指令和尋址方式,用以優化查表算法);不可避免的實時計算,算到精度夠了就結束,避免“過度”的計算;盡量使用短的數據類型,例如,盡量使用字符型的8位數據替換16位的整型數據,盡量使用分數運算而避免浮點數運算等。

2.4 讓I/O模塊間歇運行

不用的I/O模塊或間歇使用的I/O模塊要及時關掉,以節省電能。RS232的驅動需要相稱的功率,可以用單片機的一個I/O引腳來控制,在不需要通訊時,將驅動關掉。不用的I/O引腳要設置成輸出或設置成輸入,用上拉電阻拉高。由于假如引腳沒有初始化,可能會增大單片機的漏電流。特別要留意有些簡樸封裝的單片機沒有把個別I/O引腳引出來,對這些看不見的I/O引腳也不應健忘初始化。

3 結論

一個成功的低功耗設計應該是硬件設計和軟件設計的結合。從硬件設計開始,就應該充分意識到一個低功耗應用的特性,選擇一款合適的單片機,通過對其特性的了解,設計系統方案;在軟件設計上,要考慮到低功耗編程的特殊性,并盡量使用單片機的低功耗模式。

限于篇幅,僅僅討論了低功耗設計中的一些常見題目,更多的題目只能靠設計者去實際分析和解決了。

單片機為核心的嵌入式系統低功耗設計

日期:2015-01-01 文章來源:RCCN上海日成 訪問:1426

相關文章

-

電纜橋架,橋架,線槽切割機,線槽,線槽規格,線槽價格

電纜橋架,橋架,線槽切割機,線槽,線槽規格,線槽價格

-

2009第四屆中國(上海)國際母線線槽及橋架工業展覽會

金屬線槽、鍍錫母線槽、鋁合金母線槽、鋼外殼母線槽、組合式線槽、防碾壓踩踏線槽 、機械設備配電線槽、電話線槽、PVC線槽、地板線槽、插接母線線槽、微動力及照明母線槽、高中低壓電流空氣式絕緣插接母線槽、帶散熱片密集型絕緣插接式線槽、全封閉樹脂澆注母線槽(防水、防火、防腐母線槽)、共箱高低壓母線槽及軌道交通專用線槽等周邊相關加工配套產品。

-

中國品牌日:比起督促更是號角

根據企業經營規模,每年全球約有3份“世界500強”報告發布。其中《財富》雜志公布的排名,被視為最有普遍意義的榜單之一。不僅因為其拋去了“僅對發達國家企業排名”的有色眼鏡,也基于其將收入作為依據,視為衡量企業最可靠、最具證明力、也最有意義的指標。在2016年的該份榜單中,汽車行業共計22家企業入圍,其中上汽、東風、一汽、北汽、廣汽與吉利6家中國車企入選。2016年《財富》雜志世界500強中國入圍車企

-

線槽規格和品種以及線纜的敷設

線槽規格和品種以及線纜的敷設

-

低煙無鹵阻燃型走線槽

低煙無鹵阻燃型走線槽

-

PVC線槽的安裝-綜合布線

線槽安裝時,應注意與強電線槽的隔離。布線系統應避免與強電線路在無屏蔽、距離小于20cm情況下平行走3米以上。如果無法避免,該段線槽需采取屏蔽隔離措施。進入家具的電纜管線由最近的吊頂線槽沿隔墻下到地面,并從地面鏜槽埋管到家具隔斷下。

-

線槽用PVC是什么材料

在塑料制品中,線槽的主要原料是PVC.

-

線槽規格

線槽規格,上海日成-RCCN,專業制造線槽,技術團隊及豐富經驗,提供PVC線槽、行線槽、配線槽在工業設計、機械設計等配電柜綜合布線解決方案.專業服務于外資及國內品牌有線槽需求的企業,產品通過UL,CE,ROHS國際認證.

官方微信:日成最新資訊

官方微信:日成最新資訊 移動官網

移動官網 官方商城

官方商城